Number 984

# Efficient spatial and temporal safety for microcontrollers and application-class processors

Peter David Rugg

July 2023

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 2023 Peter David Rugg

This technical report is based on a dissertation submitted December 2022 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Churchill College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Efficient spatial and temporal safety for microcontrollers and application-class processors

#### Peter David Rugg

#### Abstract

This thesis discusses the implementation of Capability Hardware Enhanced RISC Instructions (CHERI) secure capabilities for RISC-V microarchitectures. This includes implementations for three different scales of core, including microcontrollers and the first open application of CHERI to a superscalar processor. Tradeoffs in developing the architecture and performant microarchitecture are investigated. The processors are then used as a platform to conduct research in reducing the overheads for achieving temporal safety with CHERI.

CHERI offers a contemporary cross-architecture description of capabilities. The initial design was previously carried out in a single MIPS processor. Based on its success in this context, this thesis investigates the microarchitectural implications across a wider range of processors. To improve adoption, this work is performed on the more contemporary RISC-V architecture. The thesis also explores the microarchitectural implications of architectural decisions arising from the adaptation of CHERI to this new context.

The first implementations are to the Piccolo and Flute microcontrollers. They present new tradeoffs, for example being the first CHERI implementations supporting a merged register file and capability mode bit. The area and frequency implications are evaluated on FPGA, and the performance and power overheads are investigated across a range of benchmarks. To validate correctness, the processors are integrated into a new TestRIG infrastructure.

This thesis also develops the first open instantiation of CHERI for a superscalar out-of-order application-class core: RiscyOO. This presents new questions due to the very different design of the more sophisticated microarchitecture, and highlights more architectural tradeoffs. Again, the processor is evaluated on FPGA, investigating area, frequency, power, and performance. This allows the first analysis of how the overheads scale differently across different sizes of core.

Finally, the augmented processors are used as a platform to refine the use of CHERI for temporal safety. Significant improvements are made to the architecture-neutral model used for revocation sweeps. In addition, processor-specific acceleration of revocation is performed, including new approaches for caching capability tags.

#### Acknowledgements

I would like to thank my supervisor—Prof. Simon W. Moore—for his patient supervision and invaluable guidance. Thanks also to Prof. Robert N. M. Watson for his advice and for driving the overall CHERI project to make this work possible.

It has been a privilege to be a part of the CHERI team and its exceptional collaborative environment. Jonathan Woodruff, Alexandre Joannou, Jessica Clarke, Franz Fuchs, Ivan Ribeiro, Nathaniel W. Filardo, Hesham Almatary, Marno van der Maas, Lawrence Esswood, A. Theodore Markettos, and everyone else: thank you for always making time for thought-provoking discussions, and for your contributions to the CHERI effort that made my work possible.

To my parents: I do not know what I would have done without your support, particularly since the pandemic. I hope you know how much this means to me.

Thank you also to my friends for being there for me along the way.

As well as my supervisor, thanks in particular to Sarah, Franz, Alexandre, Lawrence, and my parents for help with proofreading that significantly improved this thesis.

Thank you also to my examiners—Prof. David Oswald and Prof. Robert Mullins—for their time and suggestions.

Approved for public release; distribution is unlimited. This work was supported by the Defense Advanced Research Projects Agency (DARPA) under contract HR0011-18-C-0016 ("ECATS"). The views, opinions, and/or findings contained in this dissertation are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

## Contents

| G        | Glossary     |         |                                         |      |  |

|----------|--------------|---------|-----------------------------------------|------|--|

| 1        | Introduction |         |                                         |      |  |

|          | 1.1          | Archit  | sectural security                       | . 19 |  |

|          | 1.2          | Hypot   | heses                                   | . 20 |  |

|          | 1.3          | Contri  | ibutions                                | . 22 |  |

|          | 1.4          | Public  | eations                                 | . 23 |  |

|          | 1.5          | Open-   | source contributions                    | . 24 |  |

|          | 1.6          | Thesis  | s overview                              | . 25 |  |

| <b>2</b> | Bac          | kgrour  | $\operatorname{ad}$                     | 27   |  |

|          | 2.1          | Proces  | ssor design                             | . 27 |  |

|          |              | 2.1.1   | RISC-V                                  | . 28 |  |

|          |              | 2.1.2   | Bluespec                                | . 30 |  |

|          | 2.2          | Spatia  | al safety                               | . 32 |  |

|          |              | 2.2.1   | Deployed protections                    | . 32 |  |

|          |              | 2.2.2   | Related research                        | . 36 |  |

|          | 2.3          | Tempo   | oral safety                             | . 40 |  |

|          |              | 2.3.1   | Related research                        | . 41 |  |

|          | 2.4          | CHER    | RI                                      | . 44 |  |

|          |              | 2.4.1   | Model                                   | . 45 |  |

|          |              | 2.4.2   | Microarchitecture                       | . 46 |  |

|          |              | 2.4.3   | Software                                | . 48 |  |

| 3        | CH           | ERI fo  | or microcontrollers                     | 51   |  |

|          | 3.1          | Chara   | cteristics of microcontrollers          | . 51 |  |

|          | 3.2          | Baselin | ne processors                           | . 52 |  |

|          | 3.3          | Archit  | -<br>tectural changes                   | . 55 |  |

|          |              | 3.3.1   | Merged register file                    |      |  |

|          |              | 3.3.2   | Encoding mode                           | . 57 |  |

|          |              | 3.3.3   | Secure Entry capabilities               |      |  |

|          |              | 3.3.4   | CHERI-optimised compressed instructions |      |  |

|          | 3.4          |         | architectural implementation            |      |  |

|          |              | 3.4.1   | Capability decoding                     |      |  |

|   |     | 3.4.2 Bounds check                               |

|---|-----|--------------------------------------------------|

|   |     | 3.4.3 Additional instructions                    |

|   |     | 3.4.4 Cache modifications                        |

|   |     | 3.4.5 Memory subsystem changes                   |

|   |     | 3.4.6 Other changes                              |

|   | 3.5 | Flute                                            |

|   |     | 3.5.1 Branch prediction                          |

|   |     | 3.5.2 Timing                                     |

|   | 3.6 | TestRIG                                          |

|   |     | 3.6.1 QuickCheck Vengine                         |

|   |     | 3.6.2 Implementing RVFI-DII                      |

|   |     | 3.6.3 Testing with TestRIG                       |

|   |     | 3.6.4 Other verification                         |

|   | 3.7 | Future work                                      |

|   | 3.8 | Summary                                          |

| 4 | СН  | ERI microcontroller evaluation 79                |

|   | 4.1 | Baseline core information                        |

|   | 4.2 | Area                                             |

|   | 4.3 | Frequency                                        |

|   | 4.4 | Performance                                      |

|   |     | 4.4.1 Legacy performance                         |

|   |     | 4.4.2 Capability performance                     |

|   | 4.5 | Power                                            |

|   | 4.6 | Security                                         |

|   | 4.7 | Future work                                      |

|   | 4.8 | Summary                                          |

| 5 | СН  | ERI for application-class processors 101         |

|   | 5.1 | Characteristics of application-class processors  |

|   | 5.2 | Baseline processor                               |

|   | 5.3 | CHERI implementation                             |

|   |     | 5.3.1 CHERI instruction pipeline                 |

|   |     | 5.3.2 Memory pipeline                            |

|   |     | 5.3.3 PCC implementation                         |

|   |     | 5.3.4 Special Capability Register implementation |

|   |     | 5.3.5 Extending structures                       |

|   |     | 5.3.6 Safe speculation                           |

|   | 5.4 | Avoiding exceptions                              |

|   |     | 5.4.1 Fast bounds check                          |

|   | 5.5 | Software and verification 118                    |

|   | 5.6 | Future work                                  | .19 |

|---|-----|----------------------------------------------|-----|

|   | 5.7 | Summary                                      | .19 |

| 6 | CH  | ERI application-class processor evaluation 1 | 21  |

|   | 6.1 | Baseline core information                    | 121 |

|   | 6.2 | Area                                         | .22 |

|   | 6.3 | Frequency                                    | 26  |

|   | 6.4 | Performance                                  | 26  |

|   |     | 6.4.1 Legacy performance                     | 127 |

|   |     | 6.4.2 Capability performance                 | 127 |

|   |     | 6.4.3 Microcontroller benchmarks             |     |

|   | 6.5 | Power                                        | .32 |

|   | 6.6 | Security                                     |     |

|   | 6.7 | Future work                                  | 134 |

|   | 6.8 | Summary                                      |     |

| 7 | Acc | elerating temporal safety 1                  | 37  |

|   | 7.1 | High-level approach                          | 137 |

|   |     | 7.1.1 Sweeping revocation                    |     |

|   | 7.2 | Optimising sweeping revocation               |     |

|   |     | 7.2.1 Virtual memory                         |     |

|   |     | 7.2.2 As-user memory accesses                |     |

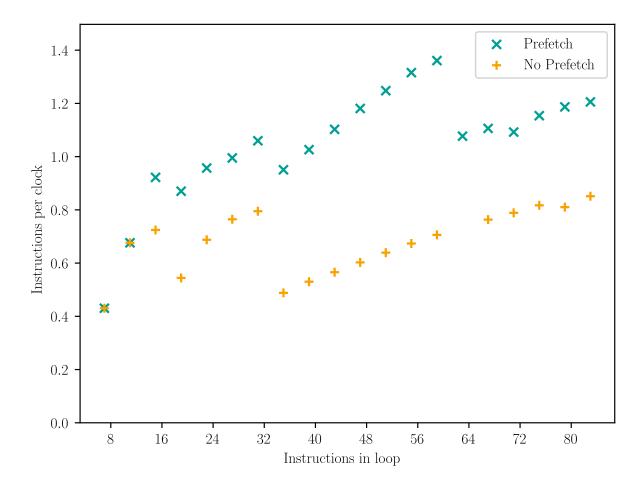

|   |     | 7.2.3 Prefetching                            |     |

|   |     | 7.2.4 Dedicated sweeper                      |     |

|   | 7.3 | Finding tags                                 |     |

|   |     | 7.3.1 Toooba memory subsystem                |     |

|   |     | 7.3.2 Initial implementation                 |     |

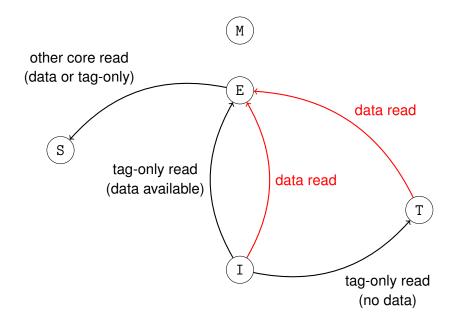

|   |     | 7.3.3 Avoiding data loads                    |     |

|   |     | 7.3.4 Avoiding cache pollution               |     |

|   |     | 7.3.5 Relaxing consistency                   |     |

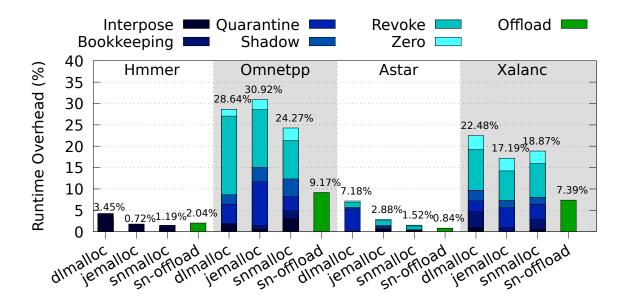

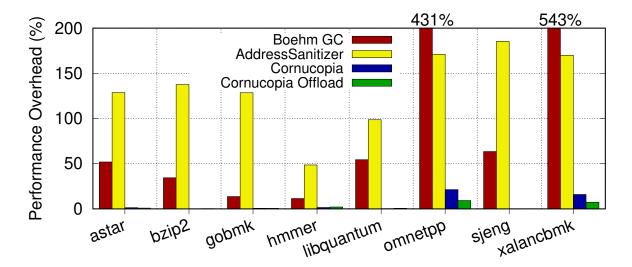

|   | 7.4 | Evaluation                                   |     |

|   | 7.5 | Alternative capability semantics             |     |

|   |     | 7.5.1 Linear capabilities                    |     |

|   |     | 7.5.2 Indirect capabilities                  |     |

|   | 7.6 | Future work                                  |     |

|   | 7.7 | Summary                                      |     |

| 8 | Cor | nclusion 1                                   | 55  |

| O | 8.1 | Answering hypotheses                         |     |

|   | 8.2 | Overall conclusions                          |     |

|   |     |                                              | 159 |

| $\mathbf{A}$ | CHERI RISC-V Instructions |                         |     |  |

|--------------|---------------------------|-------------------------|-----|--|

|              | A.1                       | Capability inspection   | 161 |  |

|              | A.2                       | Capability modification | 162 |  |

|              | A.3                       | Memory access           | 163 |  |

|              | A.4                       | Control flow            | 164 |  |

|              | A.5                       | Other instructions      | 164 |  |

| В            | Ben                       | chmarks                 | 165 |  |

|              | B.1                       | CoreMark                | 165 |  |

|              | B.2                       | MiBench                 | 165 |  |

|              | B.3                       | SPEC                    | 167 |  |

| $\mathbf{C}$ | Test                      | RIG                     | 169 |  |

| Bi           | bliog                     | graphy                  | 177 |  |

## List of Figures

| 2.1 | A simple single-element First In, First Out (FIFO) implementation in Bluespec                                                                   | 31 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | A summary of the key qualitative features of the C safety mechanisms discussed                                                                  | 40 |

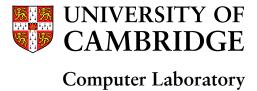

| 3.1 | The Piccolo pipeline                                                                                                                            | 53 |

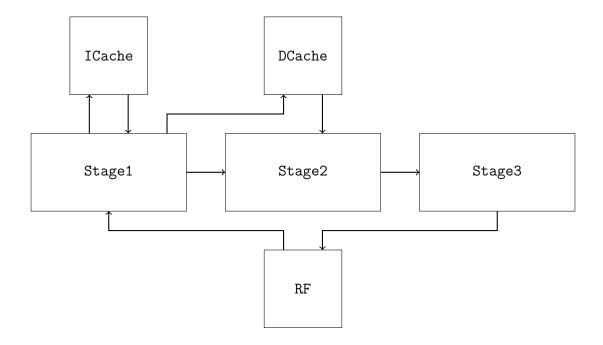

| 3.2 | The Flute pipeline                                                                                                                              | 54 |

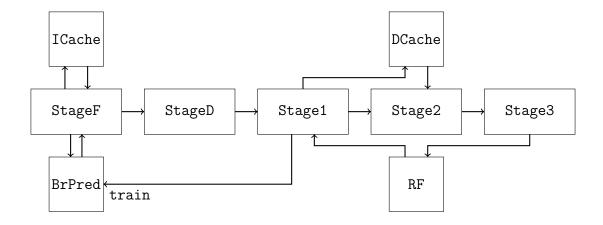

| 3.3 | Architectural view of integer and capability RISC-V registers with split and merged register files as seen by pure capability software          | 56 |

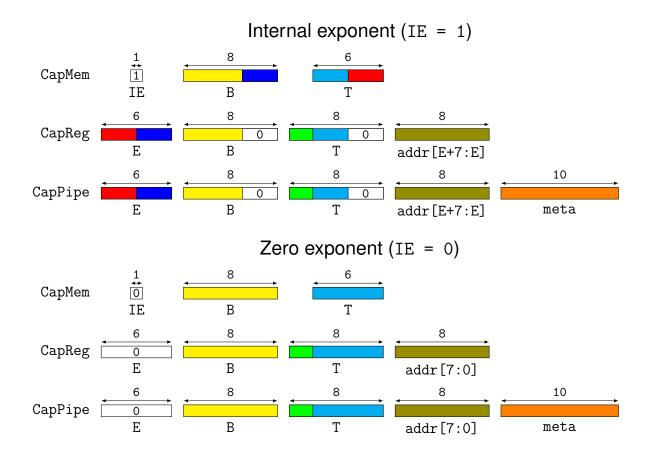

| 3.4 | Three stages of decompression of capability bounds as they enter the pipeline (RV32)                                                            | 61 |

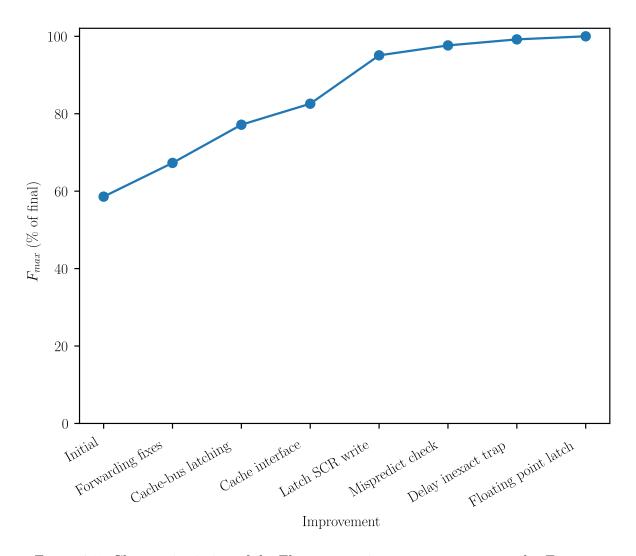

| 3.5 | Changes in timing of the Flute core as improvements were made                                                                                   | 69 |

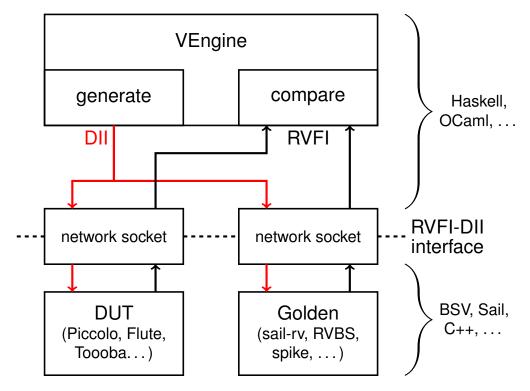

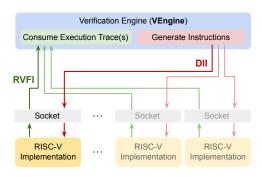

| 3.6 | The RVFI-DII interface as it connects a Vengine to implementations                                                                              | 71 |

| 4.1 | Benchmarking configuration for the Piccolo and Flute processors                                                                                 | 80 |

| 4.2 | Metrics for the baseline Piccolo and Flute cores in the evaluation System on Chip (SoC)                                                         | 80 |

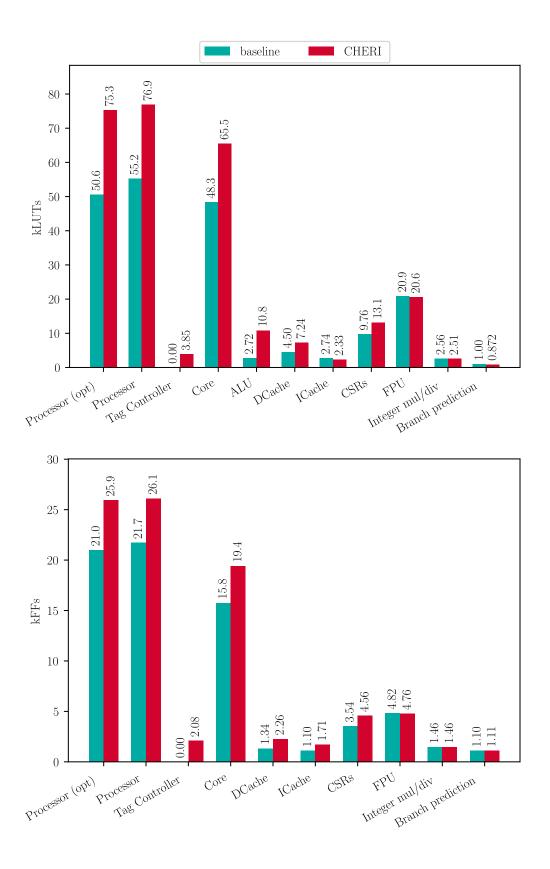

| 4.3 | Area overhead of CHERI for the Piccolo processor                                                                                                | 82 |

| 4.4 | Area overhead of CHERI for the Flute processor                                                                                                  | 83 |

| 4.5 | Number of stored bits in Piccolo and Flute structures that are hidden by BRAMs on FPGA                                                          | 84 |

| 4.6 | Maximum frequency of the Piccolo and Flute processors synthesised for the VCU-118                                                               | 87 |

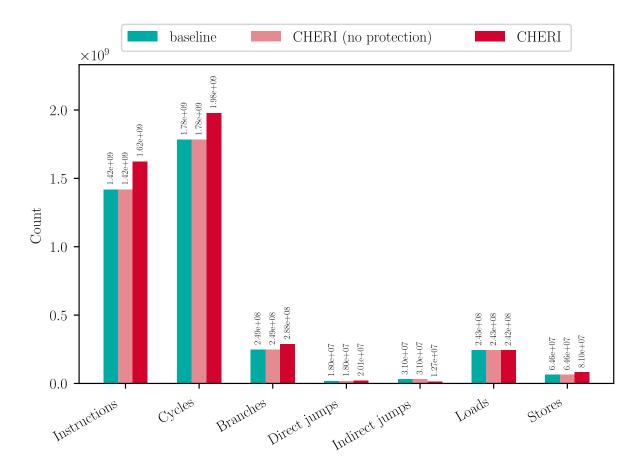

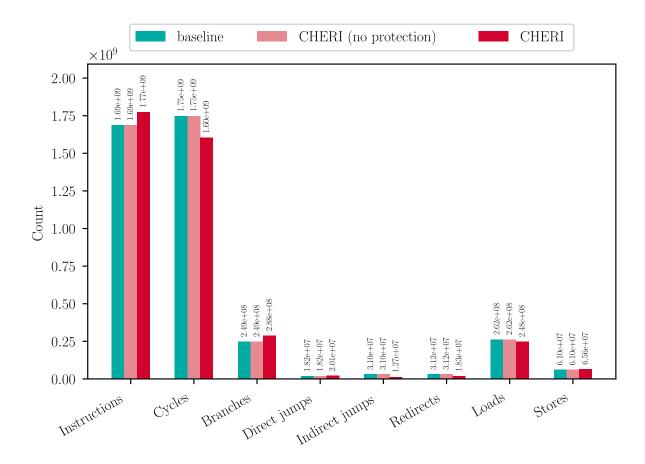

| 4.7 | CoreMark run statistics for the Piccolo baseline core, the CHERI core running the baseline software (no protection), and the CHERI core running |    |

|     | pure capability code, including relevant performance counters                                                                                   | 89 |

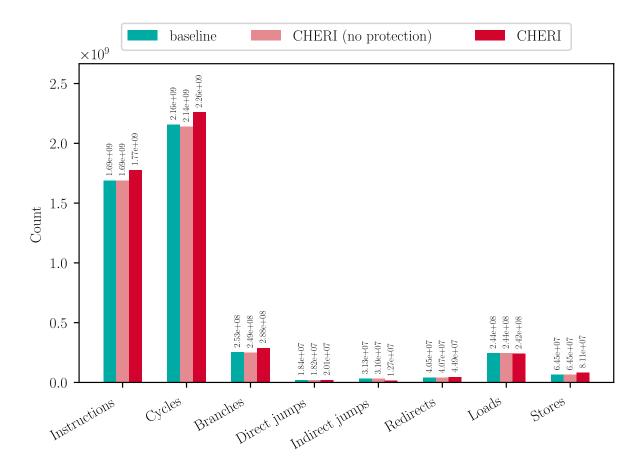

| 4.8 | CoreMark run statistics for the Flute baseline core, the CHERI core running                                                                     |    |

|     | the baseline software (no protection), and the CHERI core running pure capability code, including relevant performance counters                 | 90 |

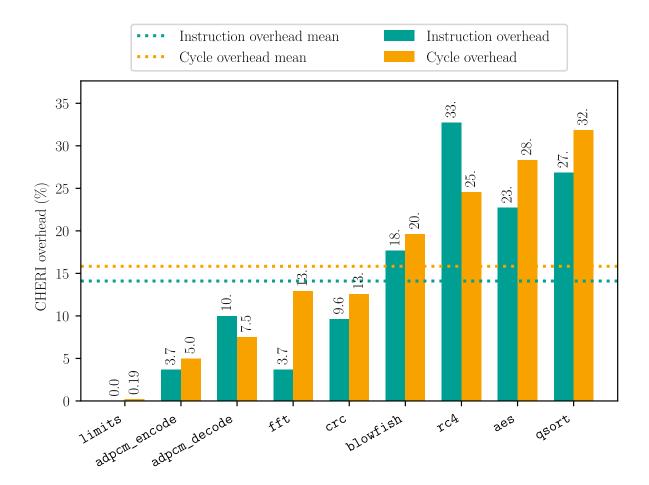

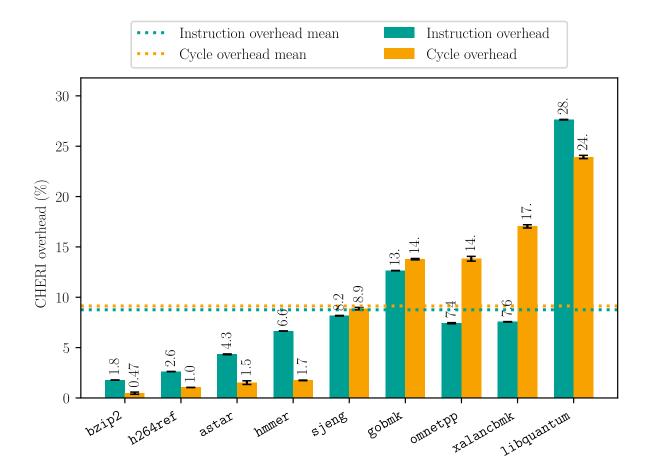

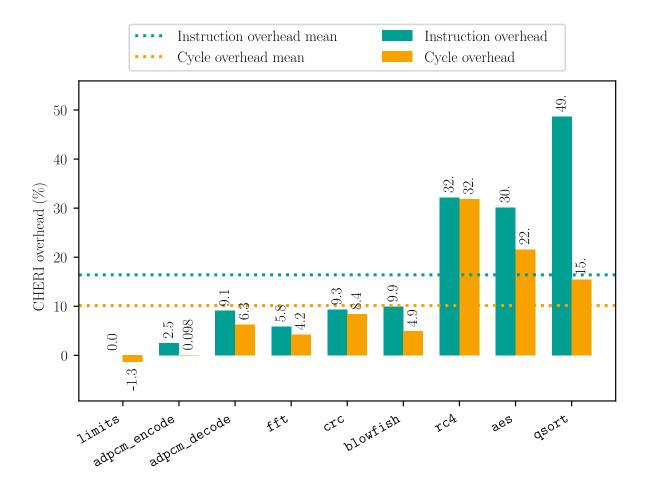

| 4.9 | MiBench overhead of CHERI for the Piccolo core                                                                                                  | 92 |

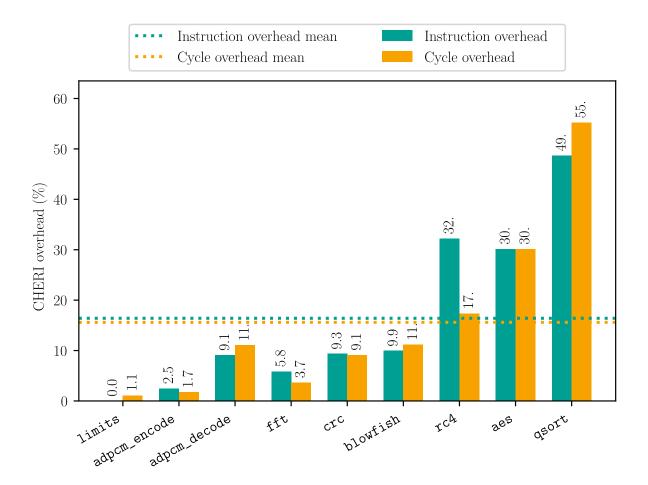

|     | MiBench overhead of CHERI for the Flute core                                                                                                    | 93 |

|     | Compiled inner loop body for the rc4 benchmark for baseline and pure                                                                            |    |

|     | capability code                                                                                                                                 | 95 |

| 4.12 | as reported by Vivado                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

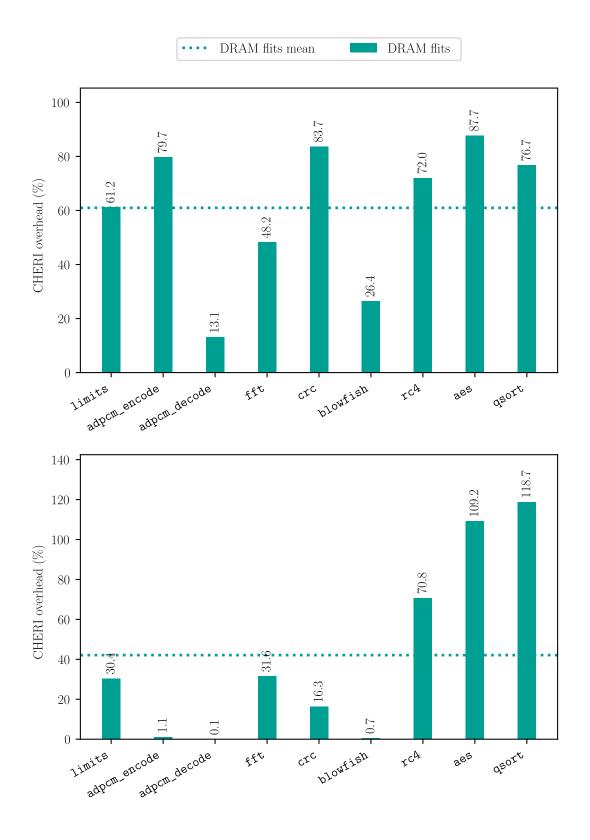

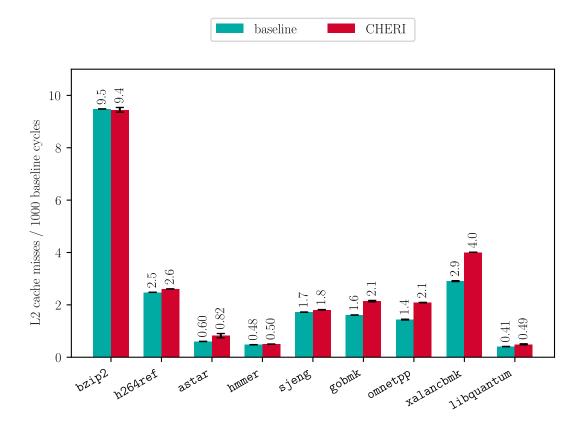

| 4.13 | MiBench DRAM traffic overhead of CHERI for the Piccolo and Flute cores.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97  |

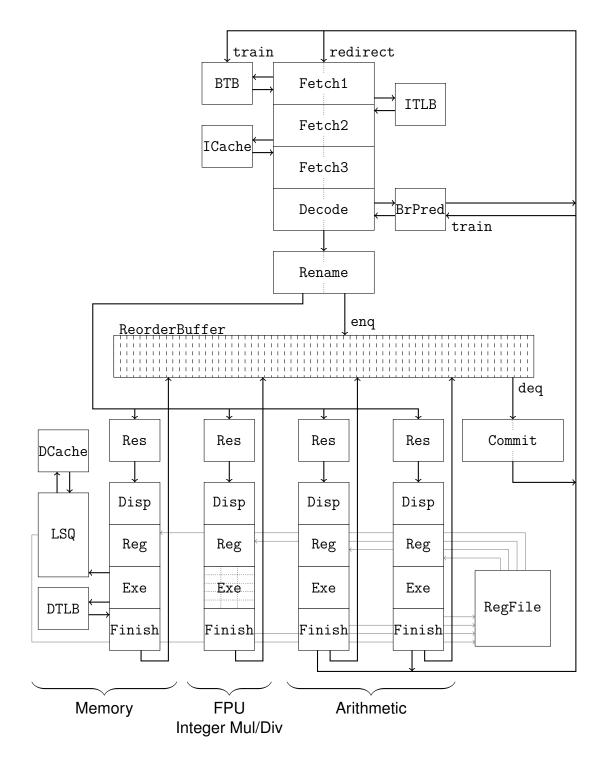

| 5.1  | The Toooba processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 103 |

| 5.2  | Usage of the Program Counter Capability (PCC) within Toooba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109 |

| 5.3  | Summary of the key Toooba structures extended to support capabilities,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | and potential optimisations to reduce the area impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111 |

| 5.4  | A CHERI RISC-V program that violates capability guarantees on Toooba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | using a speculative side channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 113 |

| 6.1  | Benchmarking configuration for the Toooba processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 122 |

| 6.2  | Metrics for the baseline Toooba core in the evaluation SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 122 |

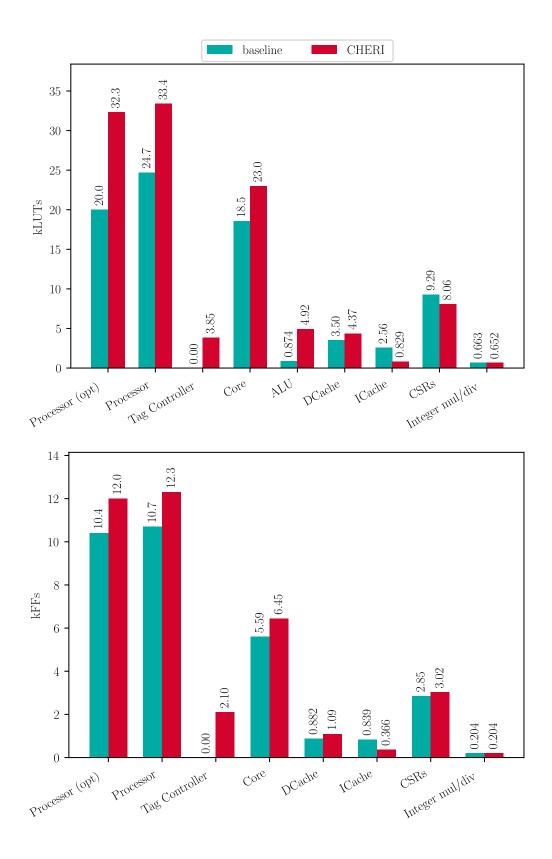

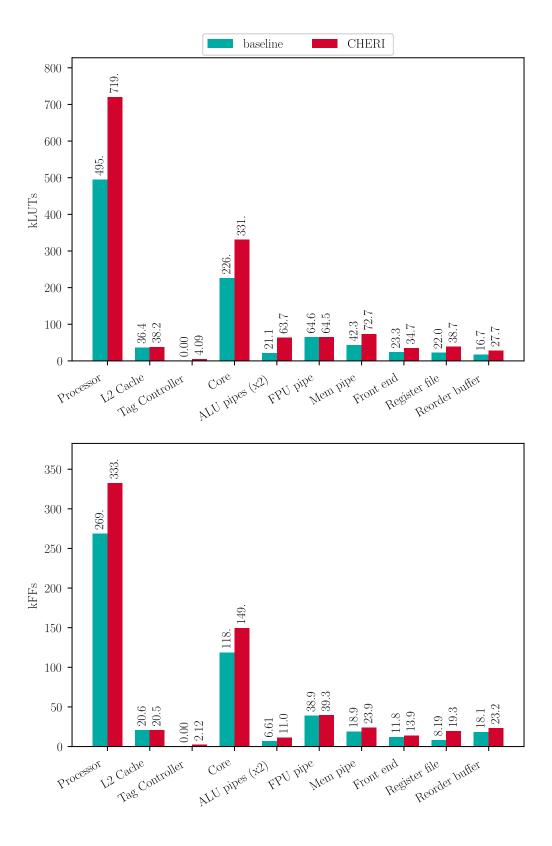

| 6.3  | Area overhead of CHERI for a dual-core Toooba processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 123 |

| 6.4  | Maximum frequency of the Toooba processor synthesised for the VCU-118. $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 126 |