Technical Report

Number 927

**Computer Laboratory**

# Capability Hardware Enhanced RISC Instructions: CHERI Instruction-Set Architecture (Version 7)

Robert N. M. Watson, Peter G. Neumann, Jonathan Woodruff, Michael Roe, Hesham Almatary, Jonathan Anderson, John Baldwin, David Chisnall, Brooks Davis, Nathaniel Wesley Filardo, Alexandre Joannou, Ben Laurie, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Kyndylan Nienhuis, Robert Norton, Alex Richardson, Peter Rugg, Peter Sewell, Stacey Son, Hongyan Xia

June 2019

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© 2019 Robert N. M. Watson, Peter G. Neumann, Jonathan Woodruff, Michael Roe, Hesham Almatary, Jonathan Anderson, John Baldwin, David Chisnall, Brooks Davis, Nathaniel Wesley Filardo, Alexandre Joannou, Ben Laurie, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Kyndylan Nienhuis, Robert Norton, Alex Richardson, Peter Rugg, Peter Sewell, Stacey Son, Hongyan Xia, SRI International

Approved for public release; distribution is unlimited. Sponsored by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL), under contracts FA8750-10-C-0237 ("CTSRD"), FA8750-11-C-0249 ("MRC2"), HR0011-18-C-0016 ("ECATS"), and FA8650-18-C-7809 ("CIFV") as part of the DARPA CRASH, MRC, and SSITH research programs. The views, opinions, and/or findings contained in this report are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of the Department of Defense or the U.S. Government. Additional support was received from St John's College Cambridge, the Google SOAAP Focused Research Award, a Google Chrome University Research Program Award, the RCUK's Horizon Digital Economy Research Hub Grant (EP/G065802/1), the EPSRC REMS Programme Grant (EP/K008528/1), the EPSRC Impact Acceleration Account (EP/K503757/1), the EPSRC IOSEC grant (EP/EP/R012458/1), the ERC Advanced Grant ELVER (789108), the Isaac Newton Trust, the UK Higher Education Innovation Fund (HEIF), Thales E-Security, Microsoft Research Cambridge, Arm Limited, Google DeepMind, HP Enterprise, and a Gates Cambridge Scholarship.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

This technical report describes CHERI ISAv7, the seventh version of the Capability Hardware Enhanced RISC Instructions (CHERI) Instruction-Set Architecture (ISA) being developed by SRI International and the University of Cambridge. This design captures nine years of research, development, experimentation, refinement, formal analysis, and validation through hardware and software implementation. CHERI ISAv7 is a substantial enhancement to prior ISA versions. We differentiate an architecture-neutral protection model vs. architecture-specific instantiations in 64-bit MIPS, 64-bit RISC-V, and x86-64. We have defined a new CHERI Concentrate compression model. CHERI-RISC-V is more substantially elaborated. A new compartment-ID register assists in resisting microarchitectural side-channel attacks. Experimental features include linear capabilities, capability coloring, temporal memory safety, and 64-bit capabilities for 32-bit architectures.

CHERI is a *hybrid capability-system architecture* that adds new capability-system primitives to commodity 64-bit RISC ISAs, enabling software to efficiently implement *fine-grained memory protection* and *scalable software compartmentalization*. Design goals include incremental adoptability within current ISAs and software stacks, low performance overhead for memory protection, significant performance improvements for software compartmentalization, formal grounding, and programmer-friendly underpinnings. We have focused on providing strong, non-probabilistic, efficient architectural foundations for the principles of *least privilege* and *intentional use* in the execution of software at multiple levels of abstraction, preventing and mitigating vulnerabilities.

The CHERI system architecture purposefully addresses known performance and robustness gaps in commodity ISAs that hinder the adoption of more secure programming models centered around the principle of least privilege. To this end, CHERI blends traditional paged virtual memory with an in-address-space capability model that includes capability registers, capability instructions, and tagged memory. CHERI builds on the C-language fat-pointer literature: its capabilities can describe fine-grained regions of memory, and can be substituted for data or code pointers in generated code, protecting data and also improving control-flow robustness. Strong capability integrity and monotonicity properties allow the CHERI model to express a variety of protection properties, from enforcing valid C-language pointer provenance and bounds checking to implementing the isolation and controlled communication structures required for software compartmentalization.

CHERI's hybrid capability-system approach, inspired by the Capsicum security model, allows incremental adoption of capability-oriented design: software implementations that are more robust and resilient can be deployed where they are most needed, while leaving less critical software largely unmodified, but nevertheless suitably constrained to be incapable of having adverse effects. Potential deployment scenarios include low-level software Trusted Computing Bases (TCBs) such as separation kernels, hypervisors, and operating-system kernels, as well as userspace TCBs such as language runtimes and web browsers. We also see potential early-use scenarios around particularly high-risk software libraries (such as data compression, protocol parsing, and image processing), which are concentrations of both complex and historically vulnerability-prone code exposed to untrustworthy data sources, while leaving containing applications unchanged.

# Acknowledgments

The authors of this report thank members of the CTSRD, MRC2, ECATS, CIFV, and REMS teams, our past and current research collaborators at SRI and Cambridge, as well as colleagues at other institutions who have provided invaluable feedback and continuing support throughout this work:

| Sam Ainsworth         | Ross J. Anderson      | Graeme Barnes      | Hadrien Barral     |

|-----------------------|-----------------------|--------------------|--------------------|

| Thomas Bauereiss      | Stuart Biles          | Matthias Boettcher | David Brazdil      |

| Ruslan Bukin          | Brian Campbell        | Gregory Chadwick   | James Clarke       |

| Serban Constantinescu | Chris Dalton          | Nirav Dave         | Dominique Devriese |

| Lawrence Esswood      | Wedson Filho          | Anthony Fox        | Paul J. Fox        |

| Paul Gotch            | Richard Grisenthwaite | Tom Grocutt        | Khilan Gudka       |

| Brett Gutstein        | Jong Hun Han          | Andy Hopper        | Alex Horsman       |

| Timothy Jones         | Asif Khan             | Myron King         | Chris Kitching     |

| Wojciech Koszek       | Robert Kovacsics      | Patrick Lincoln    | Marno van der Maas |

| Anil Madhavapeddy     | Ilias Marinos         | Tim Marsland       | Alfredo Mazzinghi  |

| Ed Maste              | Kayvan Memarian       | Dejan Milojicic    | Andrew W. Moore    |

| Will Morland          | Alan Mujumdar         | Prashanth Mundkur  | Edward Napierala   |

| Philip Paeps          | Lucian Paul-Trifu     | Colin Rothwell     | John Rushby        |

| Hassen Saidi          | Hans Petter Selasky   | Andrew Scull       | Muhammad Shahbaz   |

| Bradley Smith         | Lee Smith             | Ian Stark          | Andrew Turner      |

| Richard Uhler         | Munraj Vadera         | Jacques Vidrine    | Hugo Vincent       |

| Philip Withnall       | Bjoern A. Zeeb        |                    |                    |

The CTSRD team also thanks past and current members of its external oversight group for significant support and contributions:

| Lee Badger      | Simon Cooper        | Rance DeLong | Jeremy Epstein |

|-----------------|---------------------|--------------|----------------|

| Virgil Gligor   | Li Gong             | Mike Gordon  | Steven Hand    |

| Andrew Herbert  | Warren A. Hunt Jr.  | Doug Maughan | Greg Morrisett |

| Brian Randell   | Kenneth F. Shotting | Joe Stoy     | Tom Van Vleck  |

| Samuel M. Weber |                     |              |                |

We would also like to acknowledge the late David Wheeler and Paul Karger, whose conversations with the authors about the CAP computer and capability systems contributed to our thinking, and whose prior work provided considerable inspiration.

Finally, we are grateful to Howie Shrobe, MIT professor and past DARPA CRASH and MRC program manager, who offered both technical insight and support throughout this work. We are also grateful to Robert Laddaga, Stu Wagner, and Jonathan Smith, who succeeded Howie in overseeing the CRASH program, John Launchbury (DARPA I2O office director), Dale Waters (DARPA AEO office director), Linton Salmon (DARPA SSITH program manager), Daniel Adams and Laurisa Goergen (DARPA I2O SETAs supporting the CRASH and MRC programs), and Marnie Dunsmore and John Marsh (DARPA MTO SETAs supporting the SSITH program).

# Contents

| 1 | Intr | oduction                                           | n                                                       | 15 |  |  |

|---|------|----------------------------------------------------|---------------------------------------------------------|----|--|--|

|   | 1.1  | CHER                                               | I Design Goals                                          | 17 |  |  |

|   | 1.2  |                                                    | ecture Neutrality and Architectural Instantiations      | 18 |  |  |

|   |      | 1.2.1                                              | The Architecture-Neutral CHERI Protection Model         | 19 |  |  |

|   |      | 1.2.2                                              | An Architecture-Specific Mapping into 64-bit MIPS       | 21 |  |  |

|   |      | 1.2.3                                              | Architectural Neutrality: CHERI-RISC-V and CHERI-x86-64 | 23 |  |  |

|   | 1.3  | Determ                                             | ninistic Protection                                     | 24 |  |  |

|   | 1.4  |                                                    | I Modeling and Provable Protection                      | 24 |  |  |

|   | 1.5  | CHER                                               | I ISA Version History                                   | 25 |  |  |

|   |      | 1.5.1                                              | Changes in CHERI ISA 7.0-ALPHA1                         | 28 |  |  |

|   |      | 1.5.2                                              | Changes in CHERI ISA 7.0-ALPHA2                         | 32 |  |  |

|   |      | 1.5.3                                              | Changes in CHERI ISA 7.0-ALPHA3                         | 33 |  |  |

|   |      | 1.5.4                                              | Changes in CHERI ISA 7.0-ALPHA4                         | 35 |  |  |

|   |      | 1.5.5                                              | Changes in CHERI ISA 7.0                                | 36 |  |  |

|   | 1.6  | Experin                                            | mental Features                                         | 37 |  |  |

|   | 1.7  | Docum                                              | nent Structure                                          | 38 |  |  |

|   | 1.8  | Publica                                            | ations                                                  | 40 |  |  |

| 2 | The  | CHERI                                              | I Protection Model                                      | 45 |  |  |

|   | 2.1  | Underl                                             | ying Principles                                         | 45 |  |  |

|   | 2.2  | CHERI Capabilities: Strong Protection for Pointers |                                                         |    |  |  |

|   | 2.3  |                                                    | ectural Capabilities                                    | 48 |  |  |

|   |      | 2.3.1                                              | Tags for Pointer Integrity and Provenance               | 50 |  |  |

|   |      | 2.3.2                                              | Bounds on Pointers                                      | 51 |  |  |

|   |      | 2.3.3                                              | Permissions on Pointers                                 | 52 |  |  |

|   |      | 2.3.4                                              | Capability Monotonicity via Guarded Manipulation        | 52 |  |  |

|   |      | 2.3.5                                              | Capability Flags                                        | 53 |  |  |

|   |      | 2.3.6                                              | Sealed Capabilities                                     | 54 |  |  |

|   |      | 2.3.7                                              | Capability Object Types                                 | 54 |  |  |

|   |      | 2.3.8                                              | Sealed Capability Invocation                            | 55 |  |  |

|   |      | 2.3.9                                              | Capability Protection for Non-Pointer Types             | 55 |  |  |

|   |      | 2.3.10                                             | Capability Flow Control                                 | 56 |  |  |

|   |      | 2.3.11                                             | Capability Compression                                  | 57 |  |  |

|   |      |                                                    | Hybridization with Integer Pointers                     | 57 |  |  |

|   |      | 0 0 1 0        | TT 1 11 21 12 12 12 12 12 12 12 12 12 12 1                    | 50    |

|---|------|----------------|---------------------------------------------------------------|-------|

|   |      |                | Hybridization with Virtual Addressing                         |       |

|   |      |                | Hybridization with Architectural Privilege                    |       |

|   |      |                | Failure Modes and Exceptions                                  |       |

|   |      |                | Capability Revocation, Garbage Collection, and Flow Control   |       |

|   | 2.4  |                | re Protection and Security Using CHERI                        |       |

|   |      | 2.4.1          | Abstract Capabilities                                         |       |

|   |      | 2.4.2          | C/C++ Language Support                                        |       |

|   |      | 2.4.3          | Protecting Non-Pointer Types                                  |       |

|   |      | 2.4.4          | Isolation, Controlled Communication, and Compartmentalization |       |

|   |      | 2.4.5          | Source-Code and Binary Compatibility                          |       |

|   |      | 2.4.6          | Code Generation and ABIs                                      |       |

|   |      | 2.4.7          | Operating-System Support                                      | . 69  |

|   | 2.5  | Protect        | tion Against Microarchitectural Side-Channels                 | . 71  |

| 3 | Man  | ning Cl        | HERI Protection into Architecture                             | 73    |

| 9 | 3.1  | • · ·          | Level Architectural Goals                                     | -     |

|   | 3.2  | -              | ility-System Model                                            |       |

|   | 3.3  |                | ectural Capabilities                                          |       |

|   | 5.5  | 3.3.1          | Capability Contents                                           |       |

|   |      | 3.3.2          | Capability Values                                             |       |

|   |      | 3.3.2          | Integer Values in Capabilities                                |       |

|   |      | 3.3.3          | General-Purpose Capability Registers                          |       |

|   |      | 3.3.4          |                                                               |       |

|   | 3.4  |                | Special Capability Registers                                  |       |

|   | 5.4  | 3.4.1          | litities in Memory                                            |       |

|   |      | 3.4.1          | In-Memory Representation                                      |       |

|   |      | 3.4.2<br>3.4.3 | Tagged Memory                                                 |       |

|   |      |                | 256-bit Capability Format                                     |       |

|   |      | 3.4.4          | Compressed Capabilities                                       |       |

|   |      | 3.4.5<br>3.4.6 | CHERI Concentrate Compression                                 |       |

|   | 2.5  |                | 64-bit Capabilities for 32-bit Architectures                  |       |

|   | 3.3  |                | ility State on CPU Reset                                      |       |

|   |      | 3.5.1          | Capability Registers on Reset                                 |       |

|   | 2.6  | 3.5.2          | Tagged Memory on Reset                                        |       |

|   | 3.6  | -              | ility-Aware Instructions                                      |       |

|   | 3.7  |                | ng Failures                                                   |       |

|   | 3.8  | -              | osing Architectural Capabilities with Existing ISAs           |       |

|   |      | 3.8.1          | Architectural Privilege                                       |       |

|   |      | 3.8.2          | Traps, Interrupts, and Exception Handling                     |       |

|   |      | 3.8.3          | Virtual Memory                                                |       |

|   |      | 3.8.4          | Direct Memory Access (DMA)                                    |       |

|   | 3.9  | -              | ations for Software Models and Code Generation                |       |

|   |      | 3.9.1          | C and C++ Language and Code Generation Models                 |       |

|   |      | 3.9.2          | Object Capabilities                                           |       |

|   | 3.10 | Conclu         | Iding Notes                                                   | . 116 |

|   |      | 2 10 1 | Deep Versus Surface Design Choices                              | 116   |

|---|------|--------|-----------------------------------------------------------------|-------|

|   |      |        | Potential Future Changes to the CHERI Architecture              |       |

|   |      | 5.10.2 |                                                                 |       |

| 4 | The  | CHER   | I-MIPS Instruction-Set Architecture                             | 125   |

|   | 4.1  | The C  | HERI-MIPS ISA Extension                                         | . 126 |

|   | 4.2  | Capab  | ilities                                                         |       |

|   |      | 4.2.1  | Capability Permissions                                          |       |

|   |      | 4.2.2  | Capability Flags                                                | . 126 |

|   | 4.3  | Capab  | ility Registers                                                 | . 126 |

|   | 4.4  |        | apability Register File                                         |       |

|   | 4.5  |        | ility-Aware Instructions                                        |       |

|   | 4.6  | Capab  | ility State on CPU Reset                                        | . 129 |

|   | 4.7  | Except | tion Handling                                                   |       |

|   |      | 4.7.1  | Exception-Related Capabilities                                  | . 130 |

|   |      | 4.7.2  | Exception Temporary Special Registers                           |       |

|   |      | 4.7.3  | Capability-Related Exceptions and the Capability Cause Register |       |

|   |      | 4.7.4  | Exceptions and Indirect Addressing                              |       |

|   |      | 4.7.5  | Capability-Related Exception Priority                           |       |

|   |      | 4.7.6  | Implications for Pipelining                                     |       |

|   | 4.8  | Chang  | es to MIPS ISA Processing                                       | . 131 |

|   | 4.9  |        | es to the Translation Look-aside Buffer (TLB)                   |       |

|   | 4.10 |        | tion-Domain Transition with CCall and CReturn                   |       |

|   |      |        | CCall Selector 0 and CReturn Exception Handling                 |       |

|   |      |        | ility Register Conventions / Application Binary Interface (ABI) |       |

|   | 4.12 | Potent | ial Future Changes to the CHERI-MIPS ISA                        | . 137 |

| 5 | The  | CHER   | I-RISC-V Instruction-Set Architecture (Draft)                   | 139   |

|   | 5.1  |        | ISC-V Instruction-Set Architecture                              |       |

|   | 5.2  |        | I-RISC-V Approach                                               |       |

|   | 0.2  |        | Target RISC-V ISA Variants                                      |       |

|   |      | 5.2.2  | CHERI-RISC-V is an ISA Design Space                             |       |

|   |      | 5.2.3  | CHERI-RISC-V Strategy                                           |       |

|   |      | 5.2.4  | Architectural Features Shared with CHERI-MIPS                   |       |

|   |      | 5.2.5  | Architectural Features that Differ from CHERI-MIPS              |       |

|   | 5.3  |        | I-RISC-V Specification                                          |       |

|   |      | 5.3.1  | Tagged Capabilities and Memory                                  |       |

|   |      | 5.3.2  | Capability Register File                                        |       |

|   |      | 5.3.3  | Capability-Aware Instructions                                   |       |

|   |      | 5.3.4  | Control and Status Registers (CSRs)                             |       |

|   |      | 5.3.5  | Special Capability Registers (SCRs)                             |       |

|   |      | 5.3.6  | Efficiently Encoding Capability-Relative Operations             |       |

|   |      | 5.3.7  | Compressed Instructions                                         |       |

|   |      | 5.3.8  | Floating Point                                                  |       |

|   |      | 5.3.9  | Exception Handling                                              |       |

|   |      |        |                                                                 |       |

|   |      | 5.3.10   | Virtual Memory and Page Tables                | 154 |

|---|------|----------|-----------------------------------------------|-----|

|   |      | 5.3.11   | The RV-128 LQ, SQ, and Atomic Instructions    | 155 |

|   |      | 5.3.12   | The AUIPC Instruction                         |     |

| 6 | The  | CHERI    | -x86-64 Instruction-Set Architecture (Sketch) | 157 |

| Ŭ | 6.1  |          | lity Registers versus Segments                |     |

|   | 6.2  |          | Capabilities and Memory                       |     |

|   | 6.3  |          | ing Existing Registers                        |     |

|   | 6.4  |          | onal Capability Registers                     |     |

|   | 6.5  |          | Capabilities with Memory Address Operands     |     |

|   |      | 6.5.1    | Capability-Aware Addressing                   |     |

|   |      | 6.5.2    | Scaled-Index Base Addressing                  |     |

|   |      | 6.5.3    | RIP-Relative Addressing                       |     |

|   |      | 6.5.4    | Using Additional Capability Registers         |     |

|   | 6.6  | Capabil  | lity-Aware Instructions                       |     |

|   |      | 6.6.1    | Control-Flow Instructions                     |     |

|   |      | 6.6.2    | Manipulating Capabilities                     | 162 |

|   |      | 6.6.3    | Inspecting Tags                               | 162 |

|   | 6.7  | Capabil  | lity Violation Faults                         | 163 |

|   | 6.8  | Interrup | ot and Exception Handling                     | 163 |

|   |      | 6.8.1    | Kernel Code and Stack Capabilities            | 163 |

|   |      | 6.8.2    | Capabilities in Entry Points                  | 163 |

|   |      | 6.8.3    | SWAPGS and Capabilities                       | 164 |

|   | 6.9  | Page Ta  | ables                                         | 164 |

|   | 6.10 | Capabil  | lities and Integer Instructions               | 165 |

| 7 | The  | CHERI    | -MIPS Instruction-Set Reference               | 167 |

|   | 7.1  | Sail lan | guage used in instruction descriptions        | 167 |

|   | 7.2  |          | on Constant Definitions                       |     |

|   | 7.3  |          | on Function Definitions                       |     |

|   | 7.4  |          | f CHERI Instructions                          |     |

|   |      | CAndP    |                                               |     |

|   |      | CBEZ /   | / CBNZ                                        | 179 |

|   |      | CBTS /   | CBTU                                          | 180 |

|   |      | CCall    |                                               | 181 |

|   |      | CCheck   | kPerm                                         | 189 |

|   |      | CCheck   | kTag                                          | 190 |

|   |      | CCheck   | кТуре                                         | 191 |

|   |      |          | Regs                                          |     |

|   |      | CClear'  | Tag                                           | 195 |

|   |      |          | Ptr                                           |     |

|   |      | CGetA    | ddr                                           | 198 |

|   |      | CGetBa   | ase                                           | 199 |

|   |      | CGetC    | D                                             | 200 |

|     | CGetCause                           | . 201 |

|-----|-------------------------------------|-------|

|     | CGetLen                             | . 202 |

|     | CGetOffset                          | . 203 |

|     | CGetPCC                             | . 204 |

|     | CGetPCCSetOffset                    | . 205 |

|     | CGetPerm                            | . 206 |

|     | CGetSealed                          | . 207 |

|     | CGetTag                             | . 208 |

|     | CGetType                            | . 209 |

|     | CIncOffset                          | . 210 |

|     | CIncOffsetImm                       | . 212 |

|     | CJR / CJALR                         | . 213 |

|     | CL[BHWD][U]                         | . 215 |

|     | CLC                                 | . 218 |

|     | CLCBI                               |       |

|     | CLL[BHWD][U]                        | . 222 |

|     | CLLC                                |       |

|     | CGetAddr                            |       |

|     | CMOVZ / CMOVN                       |       |

|     | CPtrCmp: CEQ, CNE, CL[TE][U], CEXEQ |       |

|     | CReadHwr                            |       |

|     | CReturn                             |       |

|     | CS[BHWD]                            |       |

|     | CSC                                 | . 240 |

|     | CSC[BHWD]                           |       |

|     | CSCC                                |       |

|     | CSeal                               |       |

|     | CSetAddr                            |       |

|     | CSetBounds                          |       |

|     | CSetBoundsExact                     |       |

|     | CSetBoundsImm                       | 254   |

|     | CSetCause                           | . 256 |

|     | CSetCID                             |       |

|     | CSetOffset                          |       |

|     | CSub                                |       |

|     | CToPtr                              |       |

|     | CUnseal                             |       |

|     | CWriteHwr                           |       |

| 7.5 | Assembler Pseudo-Instructions       |       |

| 1.0 | 7.5.1 CGetDefault, CSetDefault      |       |

|     | 7.5.2 CGetEPCC, CSetEPCC            |       |

|     | 7.5.3 CGetKDC, CSetKDC              |       |

|     | 7.5.4 GGetKCC, CSetKCC              |       |

|     | 7.5.5 CAssertInBounds               |       |

|     |                                     | . 207 |

| CONTENTS |

|----------|

|----------|

|   |      | 7.5.6 Capability Loads and Stores of Floating-Point Values | 269 |

|---|------|------------------------------------------------------------|-----|

| 8 | Deta | iled Design Rationale                                      | 271 |

|   | 8.1  | High-Level Design Approach: Capabilities as Pointers       | 271 |

|   | 8.2  | Tagged Memory for Non-Probablistic Protection              | 272 |

|   | 8.3  | Capability Register File                                   | 274 |

|   | 8.4  | The Compiler is Not Part of the TCB for Isolated Code      |     |

|   | 8.5  | Base and Length Versus Lower and Upper Bounds              |     |

|   | 8.6  | Signed and Unsigned Offsets                                |     |

|   | 8.7  | Address Computation Can Wrap Around                        |     |

|   | 8.8  | Overwriting Capabilities in Memory                         |     |

|   | 8.9  | Reading Capabilities as Bytes                              |     |

|   |      | OTypes Are Not Secret                                      |     |

|   |      | Capability Registers are Dynamically Tagged                |     |

|   |      | Separate Permissions for Storing Capabilities and Data     |     |

|   |      | Capabilities Contain a Cursor                              |     |

|   |      | NULL Does Not Have the Tag Bit Set                         |     |

|   |      | The length of NULL is MAXINT                               |     |

|   |      | Permission Bits Determine the Type of a Capability         |     |

|   |      | Object Types Are Not Addresses                             |     |

|   |      | Unseal is an Explicit Operation                            |     |

|   |      | CMove is not Implemented as CIncOffset                     |     |

|   |      | Instruction-Set Randomization                              |     |

|   |      | System Privilege Permission                                |     |

|   | 8.22 | Composing CHERI with MIPS Exception Handling               |     |

|   |      | 8.22.1 MIPS-centric Exception Handling                     |     |

|   |      | 8.22.2 Capability Extensions to MIPS Special Registers     |     |

|   |      | 8.22.3 Kernel-Reserved Special Capability Registers        |     |

|   |      | Interrupts and CCall Selector 0 Use the Same KCC/KDC       |     |

|   |      | CCall Selector 1: Jump-Based Domain Transition             |     |

|   | 8.25 | Compressed Capabilities                                    |     |

|   |      | 8.25.1 Semantic Goals for Compressed Capabilities          |     |

|   |      | 8.25.2 Precision Effects for Compressed Capabilities       |     |

|   |      | Capability Encoding Mode                                   |     |

|   | 8.27 | Capability Encoding Mode Switching Can Be Unprivileged     | 293 |

| 9 | CHE  | CRI in High-Assurance Systems                              | 295 |

|   | 9.1  | Unpredictable Behavior                                     |     |

|   | 9.2  | Bypassing the Capability Mechanism Using the TLB           |     |

|   | 9.3  | Malformed Capabilities                                     |     |

|   | 9.4  | Constants in the Formal Model                              |     |

|   | 9.5  | Outline of Security Argument for a Reference Monitor       |     |

|   | 9.6  | CIFV                                                       | 302 |

| 10 | Rese        | earch Approach                                                   | 303 |

|----|-------------|------------------------------------------------------------------|-----|

|    | 10.1        | Motivation                                                       | 303 |

|    |             | 10.1.1 C-Language Trusted Computing Bases (TCBs)                 | 304 |

|    |             | 10.1.2 The Software Compartmentalization Problem                 | 305 |

|    | 10.2        | Methodology                                                      | 307 |

|    |             | 10.2.1 Technical Objectives and Implementation                   | 308 |

|    |             | 10.2.2 Hardware-Software-Formal Co-Design Methodology            | 308 |

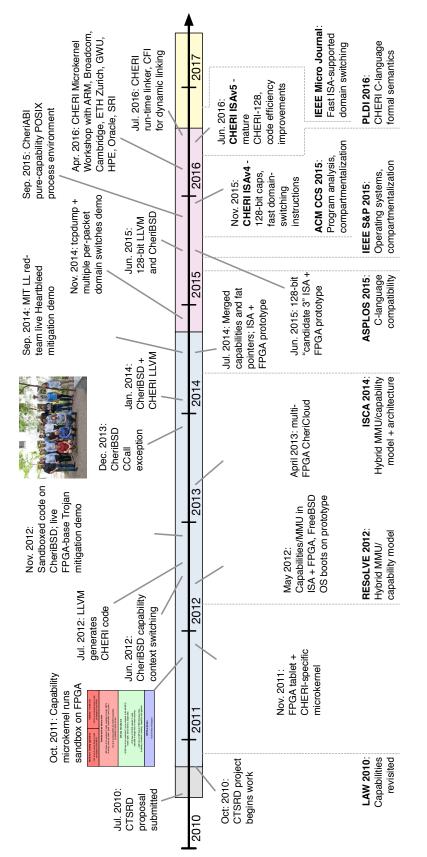

|    | 10.3        | Research and Development                                         | 310 |

|    |             | 10.3.1 CHERI ISAv7: Beyond MIPS, Temporal Safety, and Efficiency | 314 |

|    | 10.4        | A Hybrid Capability-System Architecture                          | 315 |

|    | 10.5        | A Long-Term Capability-System Vision                             | 316 |

|    | 10.6        | Threat Model                                                     | 316 |

|    | 10.7        | Formal Methodology                                               | 317 |

|    | 10.8        | Protection Model and Architecture                                | 318 |

|    | 10.9        | Hardware and Software Prototypes                                 | 319 |

| 11 | Histe       | orical Context and Related Work                                  | 321 |

|    |             | Capability Systems                                               | -   |

|    |             | Microkernels                                                     |     |

|    |             | Language and Runtime Approaches                                  |     |

|    |             | Bounds Checking and Fat Pointers                                 |     |

|    |             | Capabilities In Hardware                                         |     |

|    | 11.0        | 11.5.1 Tagged-Memory Architectures                               |     |

|    |             | 11.5.2 Segmented Architectures                                   |     |

|    | 11.6        | Influences of Our Own Past Projects                              |     |

|    |             | A Fresh Opportunity for Capabilities                             |     |

| 10 | Com         | clusion                                                          | 333 |

| 14 |             |                                                                  |     |

|    | 12.1        | Future Work                                                      | 333 |

| A  | CHE         | ERI ISA Version History                                          | 337 |

| B  | CHE         | ERI-MIPS ISA Quick Reference                                     | 361 |

|    | <b>B</b> .1 | Current Encodings                                                | 361 |

|    |             | B.1.1 Capability-Inspection Instructions                         | 361 |

|    |             | B.1.2 Capability-Modification Instructions                       | 362 |

|    |             | B.1.3 Pointer-Arithmetic Instructions                            | 362 |

|    |             | B.1.4 Pointer-Comparison Instructions                            | 362 |

|    |             | B.1.5 Exception-Handling Instructions                            | 363 |

|    |             | B.1.6 Control-Flow Instructions                                  | 363 |

|    |             | B.1.7 Assertion Instructions                                     | 363 |

|    |             | B.1.8 Special-Purpose Register access Instructions               | 364 |

|    |             | B.1.9 Fast Register-Clearing Instructions                        |     |

|    |             | B.1.10 Adjusting to Compressed Capability Precision Instructions |     |

|    |             | B.1.11 Memory-Access Instructions                                |     |

|   |             | B.1.12        | Atomic Memory-Access Instructions                     | . 365 |

|---|-------------|---------------|-------------------------------------------------------|-------|

|   |             | B.1.13        | Encoding Summary                                      | . 365 |

|   | <b>B</b> .2 | Deprec        | ated Encodings                                        | . 366 |

|   |             | B.2.1         | Capability-Inspection Instructions                    | . 366 |

|   |             | B.2.2         | Capability-Modification Instructions                  | . 367 |

|   |             | B.2.3         | Pointer-Arithmetic Instructions                       | . 367 |

|   |             | B.2.4         | Pointer-Comparison Instructions                       | . 367 |

|   |             | B.2.5         | Exception-Handling Instructions                       | . 368 |

|   |             | B.2.6         | Control-Flow Instructions                             | . 368 |

|   |             | B.2.7         | Assertion Instructions                                | . 368 |

|   |             | B.2.8         | Fast Register-Clearing Instructions                   | . 368 |

|   |             | B.2.9         | Deprecated and Removed Instructions                   | . 369 |

| С | CHI         | ERI-RIS       | SC-V ISA Quick Reference (Draft)                      | 371   |

|   | <b>C</b> .1 | Primar        | y New Instructions                                    | . 371 |

|   |             | <b>C</b> .1.1 | Capability-Inspection Instructions                    | . 371 |

|   |             | <b>C</b> .1.2 | Capability-Modification Instructions                  | . 371 |

|   |             | <b>C</b> .1.3 | Pointer-Arithmetic Instructions                       | . 372 |

|   |             | <b>C</b> .1.4 | Control-Flow Instructions                             | . 372 |

|   |             | C.1.5         | Assertion Instructions                                |       |

|   |             | <b>C</b> .1.6 | Fast Register-Clearing Instructions                   |       |

|   |             | <b>C</b> .1.7 | Memory Loads with Explicit Address Type Instructions  |       |

|   |             | <b>C</b> .1.8 | Memory Stores with Explicit Address Type Instructions |       |

|   | <b>C</b> .2 |               | ry-Access via Capability with Offset Instructions     |       |

|   |             | <b>C</b> .2.1 |                                                       |       |

|   |             | C.2.2         |                                                       |       |

|   | C.3         |               | ng Summary                                            |       |

|   | <b>C</b> .4 |               | I-RISC-V Sail definitions                             |       |

|   |             | C.4.1         | Capability Inspection                                 |       |

|   |             | C.4.2         | Capability Modification                               |       |

|   |             |               | Pointer Arithmetic                                    |       |

|   |             | C.4.4         | Control-Flow                                          |       |

|   |             | C.4.5         | Miscellaneous                                         |       |

|   |             | C.4.6         | Loads                                                 |       |

|   |             | C.4.7         | Stores                                                | . 400 |

| D | •           |               | al Features and Instructions                          | 405   |

|   | D.1         | -             | lity Flags                                            |       |

|   | D.2         | -             | lity Address and Length Rounding                      |       |

|   | D.3         |               | apability Subset Testing                              |       |

|   | D.4         |               | g Multiple Tags Without Corresponding Data            |       |

|   | D.5         |               | lity Reconstruction                                   |       |

|   |             |               | ive Mutable Load Permission                           |       |

|   | D./         | UHERI         | I-64                                                  | . 408 |

| D.7.1 CHERI-64 Encoding                                        |     |

|----------------------------------------------------------------|-----|

| D.7.2 CHERI-64/MIPS-n32 ABI                                    |     |

| D.8 Compressed Permission Representations                      |     |

| D.8.1 A Worked Example of Type Segregation                     |     |

| D.8.2 Type-segregation and Multiple Sealed Forms               |     |

| D.8.3 W <sup>X</sup> Saves A Bit                               |     |

| D.9 Memory-Capability Versioning                               | 414 |

| D.9.1 Instructions                                             | 415 |

| D.9.2 Use With System Software                                 |     |

| D.9.3 Microarchitectural Impact                                | 416 |

| D.10 Linear Capabilities                                       | 417 |

| D.10.1 Capability Linearity in Architecture                    | 417 |

| D.10.2 Capability Linearity in Software                        | 418 |

| D.10.3 Related Work in Linear Capabilities                     | 419 |

| D.11 Indirect Capabilities                                     | 419 |

| D.11.1 Indirect Capabilities in Architecture                   | 420 |

| D.11.2 Indirect Capabilities in Software                       | 420 |

| D.12 Sealed Enter Capabilities                                 | 421 |

| D.12.1 Per-Library Globals Pointers                            | 422 |

| D.12.2 Environment Calls via Enter Capabilities                | 423 |

| D.12.3 Bit Representation                                      | 423 |

| D.13 Compact Capability Coloring                               | 423 |

| D.14 Sealing With In-Memory Tokens                             | 426 |

| D.14.1 Mechanism Overview                                      | 427 |

| D.14.2 Shared VTables with Enter Capabilities and Type Tokens  | 427 |

| D.14.3 The Mechanism in More Detail                            | 428 |

| D.14.4 Unseal-Once Type Tokens                                 | 429 |

| D.14.5 User Permissions For Type-Sealed VA Capabilities        | 429 |

| D.14.6 Token-mediated CCall                                    | 430 |

| D.14.7 Hybridization                                           | 430 |

| D.15 Chaperoned Short Capabilities                             | 430 |

| D.15.1 Chaperoning Capabilities                                | 431 |

| D.15.2 Restrictions Within Short Capabilities                  | 431 |

| D.15.3 Tag Bits and Representation                             | 432 |

| D.15.4 SoCs With Mixed-Size Capabilities                       | 433 |

| D.16 Capabilities For Physical Addresses                       | 433 |

| D.16.1 Motivation                                              | 433 |

| D.16.2 Capability-Mediated CPU Physical Memory Protection      | 434 |

| D.16.3 Capability-Mediated DMA Physical Memory Protection      | 435 |

| D.16.4 Capability-Based Page Tables                            | 435 |

| D.16.5 Capability-Based Page Tables in IOMMUs                  | 436 |

| D.16.6 Exposing Capabilities Directly To Peripherals           | 436 |

| D.17 Distributed Capabilities For Peripherals And Accelerators |     |

| D.17.1 Scope and threat model                                  | 437 |

| -                                                              |     |

|             | D.17.2 Address-space coloring                    | 437 |

|-------------|--------------------------------------------------|-----|

|             | D.17.3 Capability coloring                       | 438 |

|             | D.17.4 Operations on colored capabilities        | 438 |

|             | D.17.5 Enforcement                               | 439 |

| D.18        | B Details of Proposed Instructions               | 439 |

|             | CAndAddr                                         | 440 |

|             | CBuildCap                                        | 442 |

|             | ССоруТуре                                        | 446 |

|             | CCSeal                                           | 448 |

|             | CGetAndAddr                                      | 450 |

|             | CGetFlags                                        | 451 |

|             | CLoadTags                                        | 452 |

|             | CLShC                                            | 454 |

|             | CSetFlags                                        | 455 |

|             | CSShC                                            | 456 |

|             | CTestSubset                                      | 458 |

|             | CRepresentableAlignmentMask                      | 460 |

|             | CRoundRepresentableLength                        |     |

| E CHI       | ERI-128 Compression (Deprecated)                 | 463 |

| <b>E.</b> 1 | CHERI-128 candidate 1                            | 463 |

| E.2         | CHERI-128 candidate 2 (Low-fat pointer inspired) |     |

| E.3         | CHERI-128 candidate 3                            |     |

|             | E.3.1 Implementation                             |     |

|             | E.3.2 Representable Bounds Check                 |     |

|             | E.3.3 Decompressing Capabilities                 |     |

|             | E.3.4 Bounds Alignment Requirements              |     |

| Glossar     | y                                                | 473 |

| Bibliog     | caphy                                            | 483 |

|             |                                                  |     |

# Chapter 1 Introduction

CHERI (Capability Hardware Enhanced RISC Instructions) extends commodity RISC Instruction-Set Architectures (ISAs) with new capability-based primitives that improve software robustness to security vulnerabilities. The CHERI model is motivated by the *principle of least privilege*, which argues that greater security can be obtained by minimizing the privileges accessible to running software. A second guiding principle is the *principle of intentional use*, which argues that, where many privileges are available to a piece of software, the privilege to use should be explicitly named rather than implicitly selected. While CHERI does not prevent the expression of vulnerable software designs, it provides strong *vulnerability mitigation*: attackers have a more limited vocabulary for attacks, and should a vulnerability be successfully exploited, they gain fewer rights, and have reduced access to further attack surfaces. CHERI allows software privilege to be minimized at two granularities:

- **Fine-grained code protection** CHERI provides support for *fine-grain protection* and *intentional use* through in-address-space *memory capabilities*, which replace integer virtualaddress representations of code and data pointers. The aim here is to minimize the rights available to be exercised on an instruction-by-instruction basis, limiting the scope of damage from inevitable software bugs. CHERI capabilities protect the integrity and valid provenance of pointers themselves, as well as allowing fine-grained protection of the inmemory data and code that pointers refer to. These protection policies can, to a large extent, be based on information already present in program descriptions – e.g., from Clanguage types, memory allocators, and run-time linking. This application of least privilege and intentional use provides strong protection against a broad range of memory- and pointer-based vulnerabilities and exploit techniques – buffer overflows, format-string attacks, pointer injection, data-pointer-corruption attacks, control-flow attacks, and so on. Many of these goals can be achieved through code recompilation on CHERI.

- Secure encapsulation At a coarser granularity, CHERI also supports *secure encapsulation* and *intentional use* through the robust and efficient implementation of highly scalable in-address-space *software compartmentalization* using *object capabilities*. The aim here is to minimize the set of rights available to larger isolated software components, building on efficient architectural support for strong software encapsulation. These protections are grounded in explicit descriptions of isolation and communication provided by software

authors, such as through explicit software sandboxing. This application of least privilege and intentional use provides strong mitigation of application-level vulnerabilities, such as logical errors, downloaded malicious code, or software Trojans inserted in the software supply chain.

Effective software compartmentalization depends on explicit software structure, and can require significant code change. Where compartmentalization already exists in software, CHERI can be used to significantly improve compartmentalization performance and granularity. Where that structure is not yet present, CHERI can improve the adoption path for compartmantalization due to supporting in-address-space compartmentalization models.

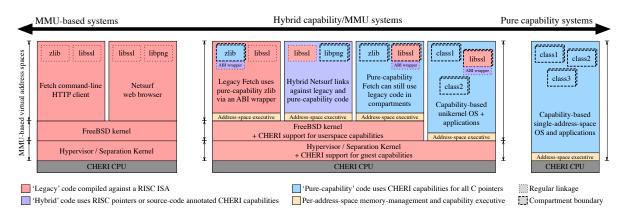

CHERI is designed to support incremental adoption within current security-critical, Clanguage *Trusted Computing Bases (TCBs)*: operating-system (OS) kernels, key system libraries and services, language runtimes supporting higher-level type-safe languages, and applications such as web browsers and office suites. While CHERI builds on many historic ideas about capability systems (see Chapter 11), one of the key contributions of this work is CHERI's *hybrid capability-system architecture*. In this context, *hybrid* refers to combining aspects from conventional architectures, system software, and language/compiler choices with capabilityoriented design. Key forms of hybridization in the CHERI design include:

- A RISC capability system A capability-system model is blended with a conventional RISC user-mode architecture without disrupting the majority of key RISC design choices.

- An MMU-enabled capability system A capability-system model is cleanly and usefully composed with conventional ring-based privilege and virtual memory based on MMUs (Memory Management Units).

- A C-language capability system CHERI can be targeted by a C/C++-language compiler with strong compatibility, performance, and protection properties.

- **Hybrid system software** CHERI supports a range of OS models including conventional MMUbased virtual-memory designs, hybridized designs that host capability-based software within multiple virtual address spaces, and pure single-address-space capability systems.

- **Incremental adoptability** Within pieces of software, capability-aware design can be disregarded, partially adopted, or fully adopted with useful and predictable semantics. This allows incremental adoption within large software bases, from OS kernels to application programs.

We hope that these hybrid aspects of the design will support gradual deployment of CHERI features in existing software, rather than obliging a clean-slate software design, thereby offering a more gentle hardware-software adoption path.

In the remainder of this chapter, we describe our high-level design goals for CHERI, the notion that CHERI is an architecture-neutral protection model with architecture-specific mappings (such as CHERI-MIPS and CHERI-RISC-V), an introduction to the CHERI-MIPS concrete instantiation, a brief version history, an outline of the remainder of this report, and our

16

#### 1.1. CHERI DESIGN GOALS

publications to date on CHERI. A more detailed discussion of our research methodology, including motivations, threat model, and evolving approach from ISA-centered prototyping to a broader architecture-neutral protection model may be found in Chapter 10. Historical context and related work for CHERI may be found in Chapter 11. The Glossary at the end of the report contains stand-alone definitions of many key ideas and terms, and may be useful reference material when reading the report.

# **1.1 CHERI Design Goals**

CHERI has three central design goals aimed at dramatically improving the security of contemporary C-language TCBs, through processor support for fine-grained memory protection and scalable software compartmentalization, whose (at times) conflicting requirements have required careful negotiation in our design:

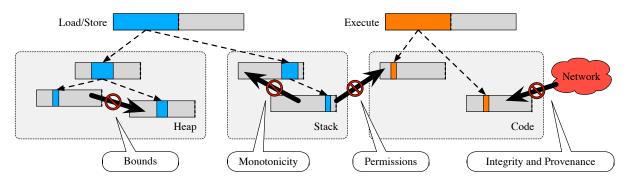

**Fine-grained memory protection** improves software resilience to escalation paths that allow low-level software bugs involving individual data structures and data-structure manipulations to be coerced into more powerful software vulnerabilities; e.g., through remote code injection via buffer overflows, control-flow and data-pointer corruption, and other memory-based techniques. Unlike MMU-based memory protection, CHERI memory protection is intended to be driven by the compiler in protecting programmer-described data structures and references, rather than via coarse page-granularity protections. CHERI capabilities limit how pointers can be used by scoping the ranges of memory (via bounds) and operations that can be performed (via permissions). They also protect the integrity, provenance, and monotonicity of pointers in order to prevent inadvertent or inappropriate manipulation that might otherwise lead to privilege escalation.

Memory capabilities may be used to implement data pointers (protecting against a variety of data-oriented vulnerabilities such as overflowing buffers) and also to implement code pointers (supporting the implementation of control-flow integrity by preventing corrupted code pointers and return addresses from being used). Fine-grained protection also provides the foundation for expressing compartmentalization within application instances. We draw on, and extend, ideas from recent work in C-language *software bounds checking* by combining *fat pointers* with capabilities, allowing capabilities to be substituted for C pointers with only limited changes to program semantics.

CHERI permits efficient implementation of dialects of C and C++ in which various invalid accesses, deemed to be undefined behavior in those languages, and potentially giving arbitrary behavior in their implementations, are instead guaranteed to throw an exception.

**Software compartmentalization** involves the decomposition of software (at present, primarily application software) into isolated components to mitigate the effects of security vulnerabilities by applying sound principles of security, such as abstraction, encapsulation, type safety, and especially least privilege and the minimization of what must be trustworthy (and therefore sensibly trusted!). Previously, it seems that the adoption of compartmentalization has been limited by a conflation of hardware primitives for virtual addressing and separation, leading to inherent performance and programmability problems when implementing fine-grained separation. Specifically, we seek to decouple the virtualization from separation to avoid scalability problems imposed by MMUs based on translation look-aside buffers (TLBs), which impose a very high performance penalty as the number of protection domains increases, as well as complicating the writing of compartmentalized software.

A viable transition path must be applicable to current software and hardware designs. CHERI hardware must be able to run most current software without significant modification, and allow incremental deployment of security improvements starting with the most critical software components: the TCB foundations on which the remainder of the system rests, and software with the greatest exposure to risk. CHERI's features must significantly improve security, to create demand for upstream processor manufacturers from their downstream mobile and embedded device vendors. These CHERI features must at the same time conform to vendor expectations for performance, power use, and compatibility to compete with less secure alternatives.

We draw on *formal methodologies* wherever feasible, to improve our confidence in the design and implementation of CHERI. This use is necessarily subject to real-world constraints of timeline, budget, design process, and prototyping, but it has helped increase our confidence that CHERI meets our functional and security requirements. Formal methods can also help to avoid many of the characteristic design flaws that are common in both hardware and software. This desire requires us not only to perform research into CPU and software design, but also to develop new formal methodologies, and adaptations and extensions of existing ones.

We are concerned with satisfying the need for trustworthy systems and networks, where *trustworthiness* is a multidimensional measure of how well a system or other entity satisfies its various requirements – such as those for security, system integrity, and reliability, as well as human safety, and total-system survivability, robustness, and resilience, notably in the presence of a wide range of adversities such as hardware failures, software flaws, malware, accidental and intentional misuse, and so on. Our approach to trustworthiness encompasses hardware and software architecture, dynamic and static evaluation, formal and non-formal analyses, good software-engineering practices, and much more.

# **1.2** Architecture Neutrality and Architectural Instantiations

CHERI consists of an architectural-neutral protection model, and a set of instantiations of that model across multiple ISAs. Our initial mapping into the 64-bit MIPS ISA has allowed us to develop the CHERI approach; we have now expanded to include a more elaborated mapping into the 64-bit RISC-V ISA, and a sketch mapping into the x86-64 ISA. In doing so, we have attempted to maximize the degree to which specification is architecture neutral, and minimize the degree to which it is architecture specific. Even within a single ISA, there are multiple potential instantiations of the CHERI protection model, which offer different design tradeoffs

- for example, decisions about whether to have separate integer and capability register files or to merge them into a single register file.

The successful mapping into multiple ISAs has led us to believe that the CHERI protection model is a portable protection model, that support portable software stacks in much the same way that portable virtual-memory-based operating systems can be implemented across a variety of architectural MMUs. Unlike MMUs, whose software interactions are primarily with the operating system, CHERI interacts directly with compiler-generated code, key system libraries, compartmentalization libraries, and applications; across all of these, we have found that an architecture-neutral approach can be highly effective, offering portability to the vast majority of CHERI-aware C/C++ code. We first consider the architecture-neutral model, and then applications of our approach in specific ISAs.

#### **1.2.1** The Architecture-Neutral CHERI Protection Model

The aim of the CHERI protection model, as embodied in both the software stack (see Chapter 2) and architecture (see Chapter 3), is to support two vulnerability mitigation objectives: first, fine-grained pointer and memory protection within address spaces, and second, primitives to support both scalable and programmer-friendly compartmentalization within address spaces. The CHERI model is designed to support low-level TCBs, typically implemented in C or a C-like language, in workstations, servers, mobile devices, and embedded devices. In contrast to MMU-based protection, this is done by protecting *references to code and data* (pointers), rather than the *location of code and data* (virtual addresses). This is accomplished via an *in-address-space capability-system model*: the architecture provides a new primitive, the *capability*, that software components (such as the OS, compiler, run-time linker, compartmentalization runtime, heap allocator, etc.) can use to implement strongly protected pointers within virtual address spaces.

In the security literature, capabilities are tokens of authority that are unforgeable and delegatable. *CHERI capabilities* are integer virtual addresses that have been extended with metadata to protect their integrity, limit how they are manipulated, and control their use. This metadata includes a *tag* implementing strong integrity protection (differentiating valid and invalid capabilities), *bounds* limiting the range of addresses that may be dereferenced, *permissions* controlling the specific operations that may be performed, and also *sealing*, used to support higher-level software encapsulation. Protection properties for capabilities include the ISA ensuring that capabilities are always derived via valid manipulations of other capabilities (*provenance*), that corrupted in-memory capabilities cannot be dereferenced (*integrity*), and that rights associated with capabilities are non-increasing (*monotonicity*).

CHERI capabilities may be held in registers or in memories, and are loaded, stored, and dereferenced using CHERI-aware instructions that expect capability operands rather than integer virtual addresses. On hardware reset, initial capabilities are made available to software via special and general-purpose capability registers. All other capabilities will be derived from these initial valid capabilities through valid capability transformations.

In order to continue to support non-CHERI-aware code, dereference of integer virtual addresses via legacy instruction is transparently indirected via a *default data capability* (**DDC**) for loads and stores, or a *program-counter capability* (**PCC**) for instruction fetch. A variety of programming-language and code-generation models can be used with a CHERIextended ISA. As integer virtual addresses continue to be supported, C or C++ compilers might choose to always implement pointers via integers, selectively implement certain pointers as capabilities based on annotations or type information (i.e., a hybrid C interpretation), or alternatively always implement pointers as capabilities except where explicitly annotated (i.e., a *pure-capability* interpretation). Programming languages may also employ capabilities internal to their implementation: for example, to protect return addresses, vtable pointers, and other virtual addresses for which capability protection can provide enhanced vulnerability mitigation.

When capabilities are being used to implement pointers (e.g., to code or data) or internal addresses (e.g., for return addresses), they must be constructed with suitably restricted rights, to accomplish effective protection. This is a run-time operation performed using explicit instructions (e.g., to set bounds, mask permissions, or seal capabilities) by the operating system, run-time linker, language runtime and libraries, and application code itself:

- **The operating-system kernel** may narrow bounds and permissions on pointers provided as part of the start-up environment when executing a program binary (e.g., to arguments or environmental variables), or when returning pointers from system calls (e.g., to new memory mappings).

- **The run-time linker** may narrow bounds and permissions when setting up code pointers or pointers to global variables.

- **The system library** may narrow bounds and permissions when returning a pointer to newly allocated heap memory.

- **The compartmentalization runtime** may narrow bounds and permissions, as well as seal capabilities, enforcing compartment isolation (e.g., to act as sandboxes).

- **The compiler** may insert instructions to narrow bounds and permissions when generating code to take a pointer to a stack allocation, or when taking a pointer to a field of a larger structure allocated as a global, on the stack, or on the heap.

- **The language runtime** may narrow bounds and permissions when returning pointers to newly allocated objects, or when setting up internal linkage, as well as seal capabilities to non-dereferenceable types.

- **The application** may request changes to permissions, bounds, and other properties on pointers, in order to further subset memory allocations and control their use.

The CHERI model can also be used to implement other higher-level protection properties. For example, tags on capabilities in memory can be used to support accurate C/C++-language temporal safety via revocation or garbage collection, and sealed capabilities can be used to enforce language-level encapsulation and type-checking features. The CHERI protection model and its implications for software security are described in detail in Chapter 2.

CHERI is an *architecture-neutral protection model* in that, like virtual memory, it can be deployed within multiple ISAs. In developing CHERI, we initially considered it as a concrete extension to the 64-bit MIPS ISA; using it, we could explore the implications downwards

into the microarchitecture, and upwards into the software stack. Having developed a mature hardware-software protection model, we used this as the baseline in deriving an architectureneutral CHERI protection model. This architecture-neutral model is discussed in detail in Chapter 3. We have demonstrated the possibility of adding CHERI protection to more than one base ISA by providing a detailed concrete instantiation for the 64-bit MIPS ISA (Chapter 4), a draft instantiation in the RISC-V ISA (Chapter 5), and a lightweight architectural sketch for the x86-64 ISA (Chapter 6).

# 1.2.2 An Architecture-Specific Mapping into 64-bit MIPS

The CHERI-MIPS ISA (see Chapter 4) is an instantiation of the CHERI protection model as an extension to the 64-bit MIPS ISA [50]. CHERI adds the following features to the MIPS ISA<sup>1</sup> to support granular memory protection and compartmentalization within address spaces:

**Capability registers** describe the rights (*protection domain*) of the executing thread to access memory, and to invoke object references to transition between protection domains. We model these registers as a separate *capability register file*, supplementing the general-purpose integer register file.

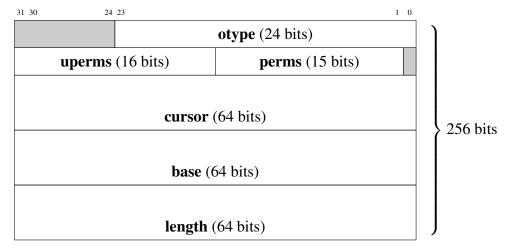

Capability registers contain a tag, object type, permission mask, base, length, and offset (allowing the description of not just a bounded region, but also a pointer into that region, improving C-language compatibility). Capability registers are suitable for describing both data and code, and can hence protect both data integrity/confidentiality and control flow. Certain registers are reserved for use in exception handling; all others are available to be managed by the compiler using the same techniques used with conventional registers. Over time, we imagine that software will increasingly use capabilities rather than integers to describe data and object references.

Another potential integration into the ISA (which would maintain the same CHERI protection semantics) would be to extend the existing general-purpose integer registers so that they could also hold capabilities. This might reduce the hardware resources required to implement CHERI support. However, we selected our current approach to maintain consistency with the MIPS ISA extension model (in which coprocessors have independent register files), and to minimize *Application Binary Interface (ABI)* disruption on boundaries between legacy and CHERI-aware code for the purposes of rapid architectural and software iteration. We explore the potential space of mappings from the CHERI model into the ISA in greater detail in Section 3.10.1, as well as in Chapters 5 and 6 where we consider alternative mappings into non-MIPS ISAs.

**Capability instructions** allow executing code to create, constrain (e.g., by reducing bounds or permissions), manage, and inspect capability register values. Both unsealed (memory) and sealed (object) capabilities can be loaded and stored via memory capability registers

<sup>&</sup>lt;sup>1</sup>Formally, CHERI instructions are added to MIPS as a *MIPS coprocessor* – a reservation of opcode space intended for third-party use. Despite the suggestive term "coprocessor", CHERI support will typically be integrated tightly into the processor pipeline, memory subsystem, and so on. We therefore eschew use of the term.

(i.e., dereferencing). Object capabilities can be invoked, via special instructions, allowing a transition between protection domains, but are *immutable* and *non-dereferenceable*, providing encapsulation of the code or data that they refer to. Capability instructions implement *guarded manipulation*: invalid capability manipulations (e.g., to increase rights or length) and invalid capability dereferences (e.g., to access outside of a bounds-checked region) result in an exception that can be handled by the supervisor or language runtime. A key aspect of the instruction-set design is *intentional use of capabilities*: explicit capability registers, rather than ambient authority, are used to indicate exactly which rights should be exercised, to limit the damage that can be caused by exploiting bugs. Tradeoffs exist around intentional use, and in some cases compatibility or opcode utilization may dictate implicit capability selection; for example, legacy MIPS load and store instructions implicitly register. Most capability instructions are part of the user-mode ISA, rather than the privileged ISA, and will be generated by the compiler to describe application data structures and protection properties.

**Tagged memory** associates a 1-bit tag with each capability-aligned and capability-sized word in physical memory, which allows capabilities to be safely loaded and stored in memory without loss of integrity. Writes to capability values in memory that do not originate from a valid capability in the capability register file will clear the tag bit associated with that memory, preventing accidental (or malicious) dereferencing of invalid capabilities.

This functionality expands a thread's effective protection domain to include the transitive closure of capability values that can be loaded via capabilities via those present in its register file. For example, a capability register representing a C pointer to a data structure can be used to load further capabilities from that structure, referring to further data structures, which could not be accessed without suitable capabilities.

Non-bypassable tagging of unforgeable capabilities enables not only reliable and secure enforcement of capability properties, but also reliable and secure identification of capabilities in memory for the purposes of implementing other higher-level protection properties such as temporal safety.

In keeping with the RISC philosophy, CHERI instructions are intended for use primarily by the operating system and compiler rather than directly by the programmer, and consist of relatively simple instructions that avoid (for example) combining memory access and register value manipulation in a single instruction. In our current software prototypes, there are direct mappings from programmer-visible C-language pointers to capabilities in much the same way that conventional code generation translates pointers into general-purpose integer register values; this allows CHERI to continuously enforce bounds checking, pointer integrity, and so on. There is likewise a strong synergy between the capability-system model, which espouses a separation of policy and mechanism, and RISC: CHERI's features make possible the implementation of a wide variety of OS, compiler, and application-originated policies on a common protection substrate that optimizes fast paths through hardware support.

Our prototype of this approach, instantiating our ideas about CHERI capability access to a specific instruction set (the 64-bit MIPS ISA) has necessarily led to a set of congruent imple-

#### 1.2. ARCHITECTURE NEUTRALITY AND ARCHITECTURAL INSTANTIATIONS 23

mentation decisions about register-file size, selection of specific instructions, exception handling, memory alignment requirements, and so on, that reflect that starting-point ISA. These decisions might be made differently with another starting-point ISA as they are simply surface features of the underlying approach; we anticipate that adaptations to ISAs such as ARM, RISC-V, and x86-64 would adopt instruction-encoding conventions, and so on, more in keeping with their specific flavor and design (see Chapters 5 and 6).

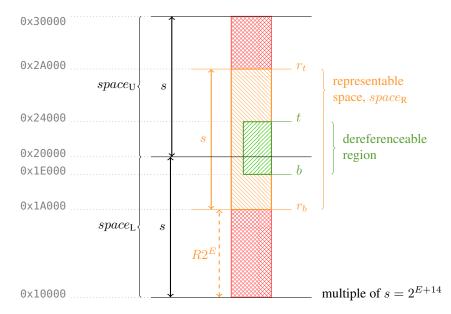

Other design decisions reflect the goal of creating a platform for prototyping and exploring the design space itself; among other choices, this includes the initial selection of 256-bit capabilities, giving us greater flexibility to experiment with various bounds-checking and capability behaviors. However, a 256-bit capability introduces potentially substantial cache overhead for pointer-intensive applications – so we have also developed a "compressed" 128-bit in-memory representation. This approach exploits redundancy between the virtual address represented by a capability and its lower and upper bounds – but necessarily limits granularity, leading to stronger alignment requirements.

In our CHERI-MIPS prototype implementation of the CHERI model, capability support is tightly coupled with the existing processor pipeline: instructions propagate values between general-purpose integer registers and capability registers; capabilities transform interpretation of virtual addresses generated by capability-unaware instructions including by transforming the program counter; capability instructions perform direct memory stores and loads both to and from general-purpose integer registers and capability registers; and capability-related behaviors deliver exceptions to the main pipeline. By virtue of having selected the MIPS-centric design choice of exposing capabilities as a separate set of registers, we maintain a separate capability register file as an independent hardware unit – in a manner comparable to vector or floating-point units in current processor designs. The impacts of this integration include additional control logic due to maintaining a separate register file, and a potentially greater occupation of opcode space, whereas combining register files might permit existing instructions to be reused (with care) across integer and capability operations.

Wherever possible, CHERI systems make use of existing hardware designs: processor pipelines and register files, cache memory, system buses, commodity DRAM, and commodity peripheral devices such as NICs and display cards. We are currently focusing on enforcement of CHERI security properties on applications running on a general-purpose processor; in future work, we hope to consider the effects of implementing CHERI in peripheral processors, such as those found in Network Interface Cards (NICs) or Graphical Processing Units (GPUs).

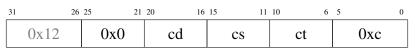

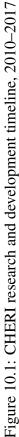

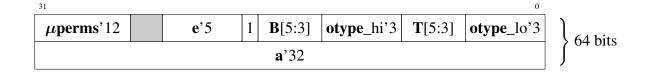

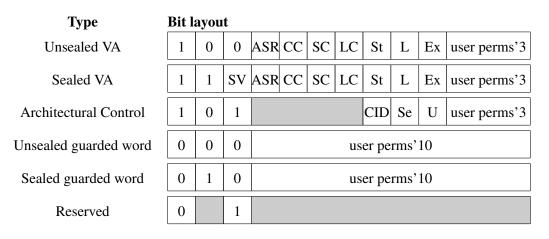

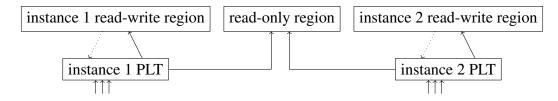

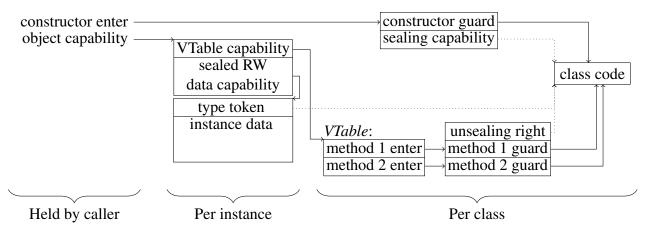

#### 1.2.3 Architectural Neutrality: CHERI-RISC-V and CHERI-x86-64